(The particular 31- or 93-step sequence depends on where in the 32767-step sequence the shift register was when Mode flag was set). This results in a pseudo-random bit sequence, 32767 steps long when Mode flag is clear, and randomly 93 or 31 steps long otherwise. The shift register is shifted right by one bit.īit 14, the leftmost bit, is set to the feedback calculated earlier. When the timer clocks the shift register, the following actions occur in order:įeedback is calculated as the exclusive-OR of bit 0 and one other bit: bit 6 if Mode flag is set, otherwise bit 1. $400F - Length counter load and envelope restart (write) The noise channel contains the following: envelope generator, timer, Linear Feedback Shift Register, length counter. The NES APU noise channel generates pseudo-random 1-bit noise at 16 different frequencies.

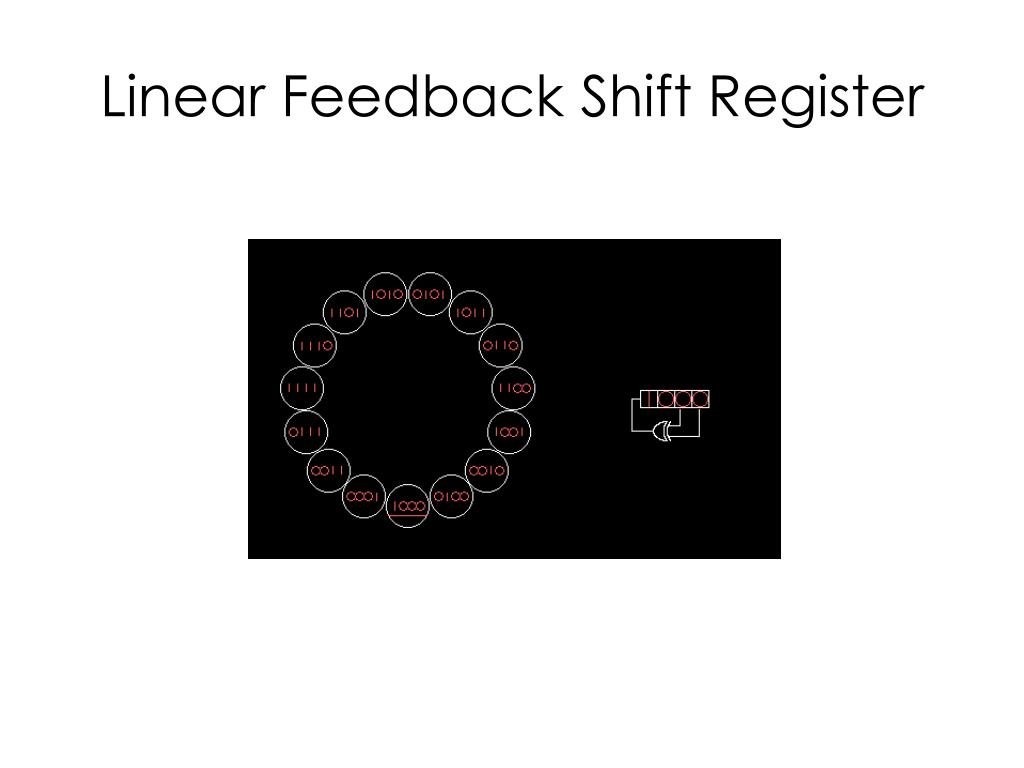

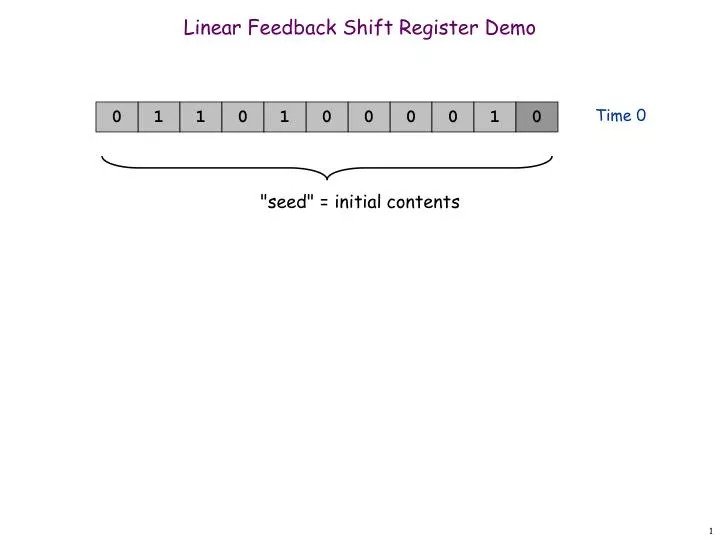

The mathematics of a cyclic redundancy check, used to provide a quick check against transmission errors, are closely related to those of an LFSR. Both hardware and software implementations of LFSRs are common. However, an LFSR with a well-chosen feedback function can produce a sequence of bits that appears random and has a very long cycle.Īpplications of LFSRs include generating pseudo-random numbers, pseudo-noise sequences, fast digital counters, and whitening sequences. Likewise, because the register has a finite number of possible states, it must eventually enter a repeating cycle. The initial value of the LFSR is called the seed, and because the operation of the register is deterministic, the stream of values produced by the register is completely determined by its current (or previous) state. Thus, an LFSR is most often a shift register whose input bit is driven by the XOR of some bits of the overall shift register value.

The most commonly used linear function of single bits is exclusive-or (XOR). In computing, a linear-feedback shift register ( LFSR) is a shift register whose input bit is a linear function of its previous state.

0 kommentar(er)

0 kommentar(er)